micron. Educator Hub

## Intro to Memory Packaging

Reviewed: 2025

© 2024-2025 Micron Technology, Inc. All rights reserved. Information, products, and/or specifications are subject to change without notice. All information is provided on an "AS IS" basis without warranties of any kind. Statements regarding products, including statements regarding product features, availability, functionality, or compatibility, are provided for informational purposes only and do not modify the warranty, if any, applicable to any product. Drawings may not be to scale. Micron, the Micron logo, and other Micron trademarks are the property of Micron Technology, Inc. All other trademarks are the property of their respective owners.

### **Copyright guidelines**

By using any content provided by the Micron Educator Hub, you acknowledge that Micron Technology, Inc. ("Micron") is the sole owner of the content and agree that any use of the content provided by the Micron Educator Hub must comply with applicable laws and require strict compliance with these Guidelines:

- 1. Credit shall be expressly stated by you to Micron for use of the content, including any portion thereof, as follows:

- a. "© 2024-2025 Micron Technology, Inc. All Rights Reserved. Used with permission."

- 2. You may not use the content in any way or manner other than for educational purposes.

- 3. You may not modify the content without approval by Micron.

- 4. You may not use the content in a manner which disparages or is critical of Micron, its employees, or Micron's products/services.

- 5. Permission to use the content may be canceled/terminated by Micron at any time upon written notice from Micron to You if You fail to comply with the terms herein.

- 6. You acknowledge and agree that the content is provided by Micron to You on an "as is" basis without any representations or warranties whatsoever, and that Micron shall have no liability whatsoever arising from Your use of the content. Micron shall ensure that the content does not violate any statutory provisions and that no rights of third parties are infringed by the content or its publication. Otherwise, liability of the parties shall be limited to intent and gross negligence.

- 7. You acknowledge and agree that the content is the copyrighted material of Micron and that the granting of permission by Micron to You as provided for herein constitutes the granting by Micron to You of a non-exclusive license to use the content strictly as provided for herein and shall in no way restrict or affect Micron's rights in and/or to the content, including without limitation any publication or use of the content by Micron or others authorized by Micron.

- 8. Except for the above permission, Micron reserves all rights not expressly granted, including without limitation any and all patent and trade secret rights. Except as expressly provided herein, nothing herein will be deemed to grant, by implication, estoppel, or otherwise, a license under any of Micron's other existing or future intellectual property rights.

#### How to cite sources from the Micron Educator Hub

- Micron is committed to collaborate with educators to make semiconductor memory education resources available through the Micron Educator Hub

- The content in the Micron Educator Hub has been identified by Micron as current and relevant to our company

- Please refer to the table on the right for proper citation

| Use case                                                                                               | How to cite sources                                                   |  |

|--------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|--|

| a) Whole slide deck or whole<br>document                                                               | No additional citation required                                       |  |

| Description: User uses the whole slide<br>deck or whole document AS IS,<br>without any modification    |                                                                       |  |

| b) Full slide or full page                                                                             | © 2020-2025 Micron Technology, Inc.<br>All Rights Reserved. Used with |  |

| Description: User incorporates a full<br>slide or a full page into their own slide<br>deck or document | permission."                                                          |  |

| c) Portion of a slide or portion of a page                                                             | This is not allowed                                                   |  |

| Description: User copies a portion of a slide or a portion of a page into a new slide or page          |                                                                       |  |

#### **Table of Contents**

- **1** Goal, Objectives and Target Audience

- **2** Introduction to Packaging

- **3** Diverse Ecosystem and Knowledge Base for a Successful Packaging Team

- 4 Purpose of Packaging

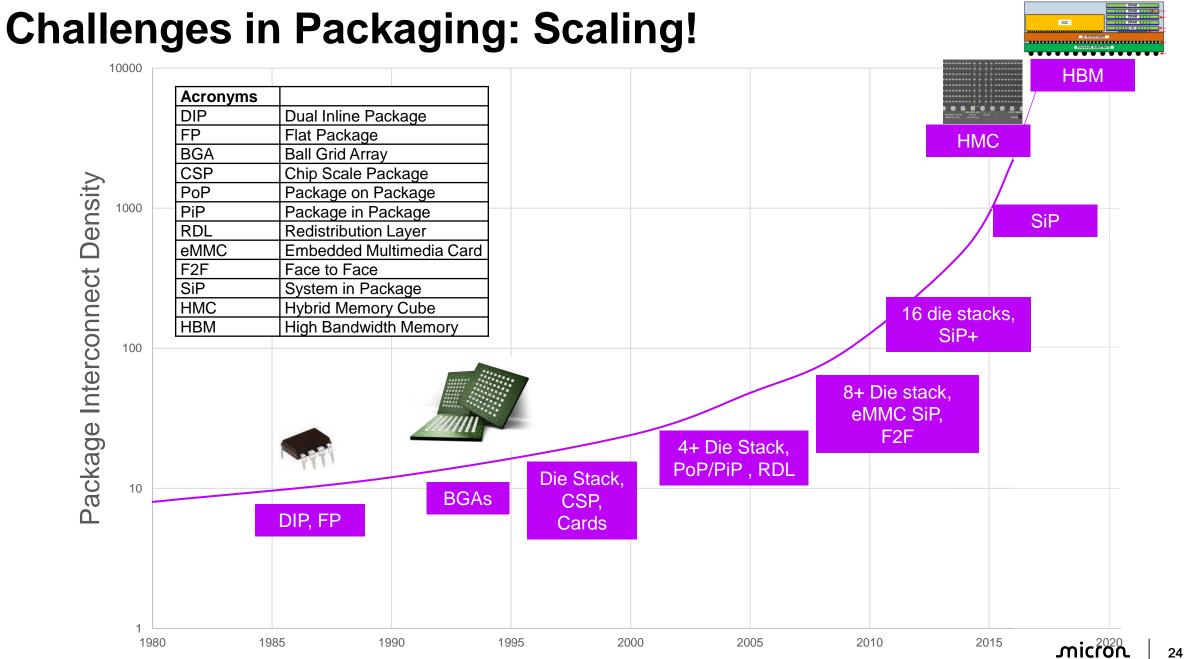

- **5** Scaling Challenges in Packaging

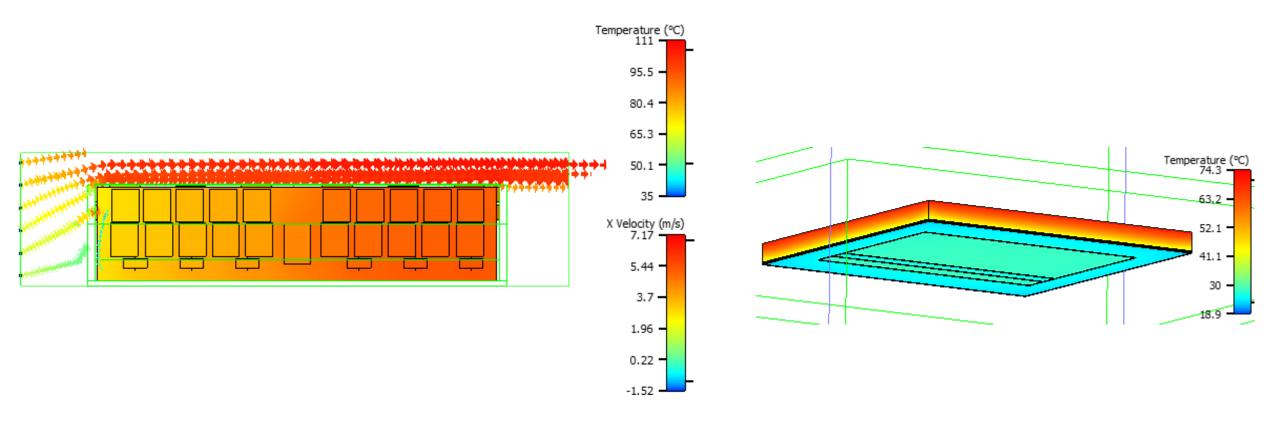

- **6** Thermal Simulations in Packaging

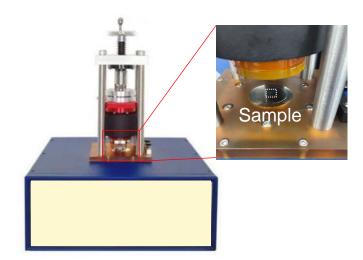

- 7 Lab Testing in Packaging

- 8 Glossary and Key Terminology

#### **Introduction to Packaging - Goal and Objectives**

Participants will learn the role packaging plays in semiconductor manufacturing, the diverse ecosystem and knowledge base required for a successful packaging team, and industry trends in packaging.

#### **Objectives:**

- 1. Describe the different types of packaging technology used in semiconductor memory

- 2. Explain the purpose of packaging in semiconductor memory technology

- 3. Explain challenges in semiconductor packaging as technology scales

- 4. Describe lab testing performed on packaging

- 5. Understand the importance of a diverse ecosystem and knowledge base for a successful packaging team

#### **Target Audience**

- This Introduction to Packaging module covers the basics of Semiconductor packaging.

- Interns, NCGs (New College Grads), and new employees in technical roles need to understand these concepts

- Examples of critical target audience roles at Micron that utilize these concepts:

- Packaging Engineer

- Packaging Integration Engineer

- Packaging Operations Engineer

- Packaging Equipment Engineer

- Process Technicians

- Equipment Technicians

- Process Engineer

- Equipment Engineer

- Process Integration Engineer

- Product Engineer

- Characterization Engineer

- Yield Enhancement Engineer

- Test Engineer

- Probe Engineer

- Reliability Engineer

- Quality Engineer

- Design Engineer

- Verification Engineer

#### **Pro tip**

Everyone interviewing at Micron can use this presentation to prepare for the interview by learning foundational information about memory. Check out the candidate guides for Engineering, Technician and Business roles.

- Micron engineering candidate guide

- <u>Micron technician candidate guide</u>

- Micron business candidate guide

## Introduction to Memory Packaging

### **Introduction to Packaging**

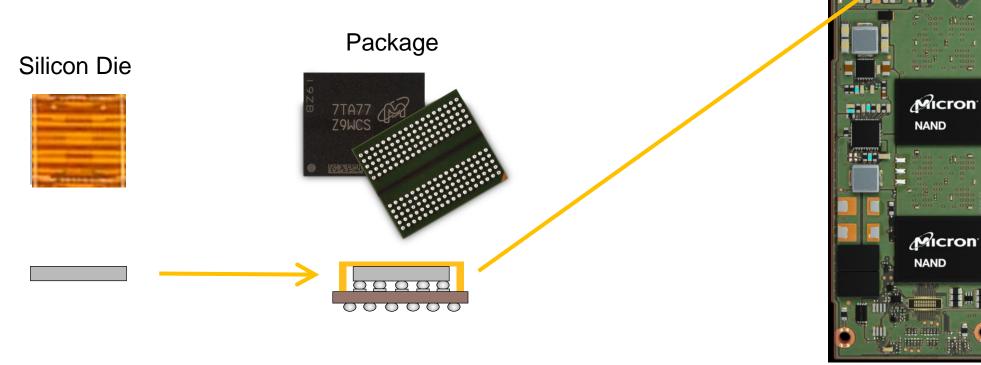

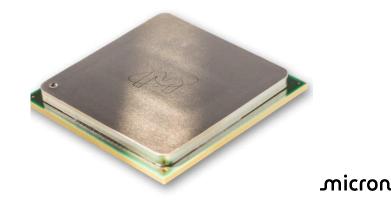

The semiconductor package is the components surrounding a memory die that enables its use in circuitry.

**Circuit Board**

Micro

### **Semiconductor Memory Manufacturing Flow**

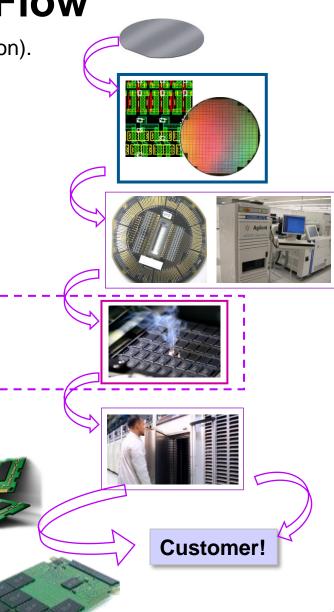

**Start Material:** Silicon is purified and formed into wafers (outside Micron).

<u>Wafer-Level Fabrication</u>: Electronic devices (transistors, resistors, capacitors, etc.) are fabricated on the silicon wafers, and are then interconnected together into complete circuits.

**Probe**: Each die is tested for functionality, failing die are flagged. Failure data (bins) is collected for yield improvement. **Param**: Wafer-level electrical data is collected to characterize and improve the process.

This document focuses on this part

**Packaging**: Die that pass Probe are separated from the wafer and assembled into packages.

**Final Test and Burn-In**: Packaged parts are tested for functionality. Some parts are given additional tests under harsh conditions to verify

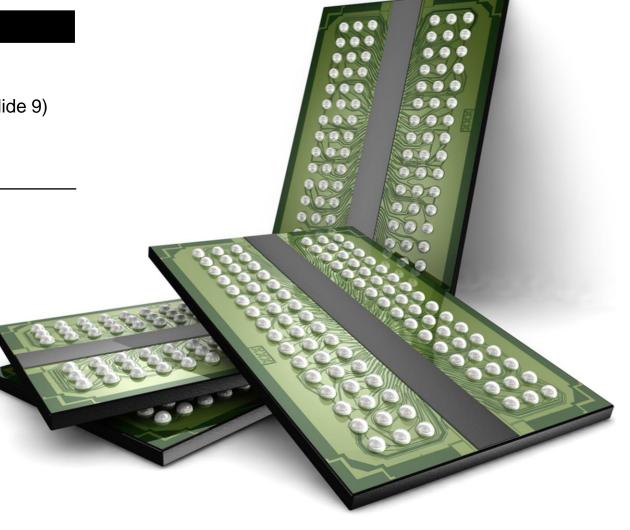

**Module Assembly and Testing**: Some DRAM packaged parts are placed into modules and further tested for functionality and reliability.

**System/SSD Testing**: NAND packaged parts may be placed into SSDs or Composite drives and further tested for performance.

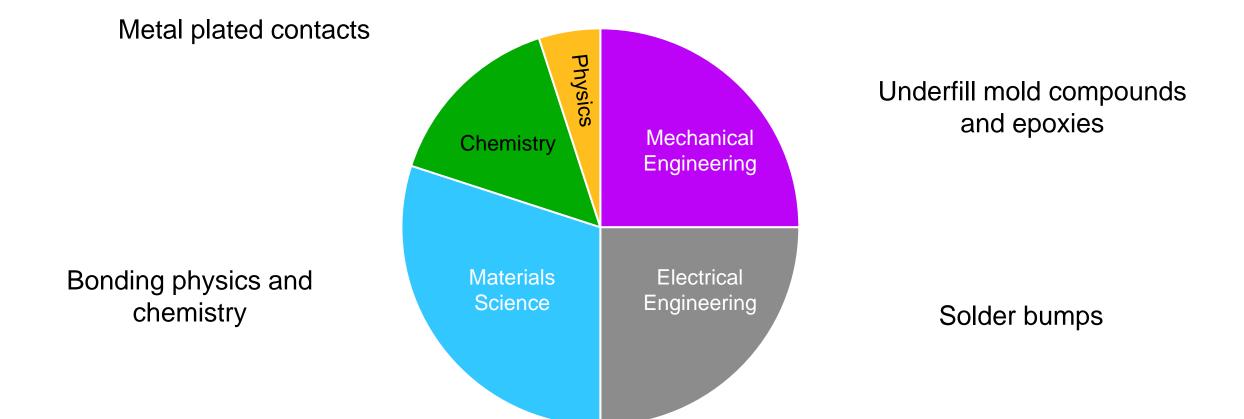

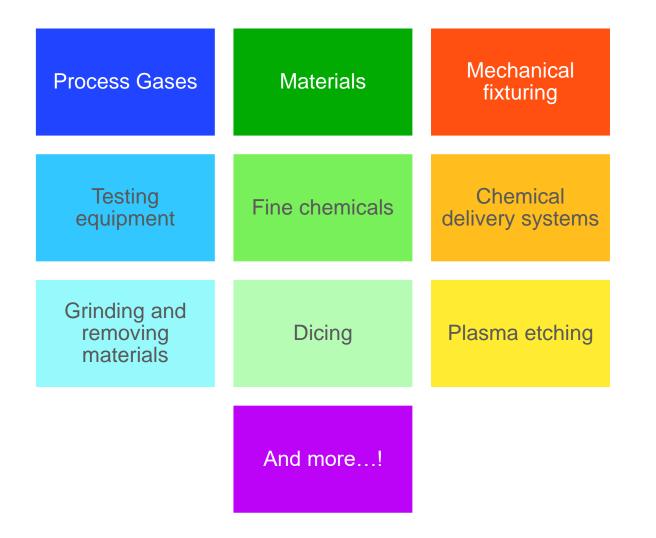

#### What goes into making Semiconductor Packages?

Silicon integrated circuits

#### **Additional Tasks**

Very diverse ecosystem and knowledge base to develop and deploy semiconductor packaging!

#### **Engineering Disciplines in Packaging**

Tackling challenges in packaging requires a diverse educational background

- <u>Mechanical Engineering</u>: Evaluate package warpage, mechanical integrity, thermal characterization.

- <u>Electrical Engineering</u>: Design and evaluate electrical routing of die and interposers in the package.

- <u>Materials Science</u>: Chemistry, metallurgy, and innovations in material science drive many of the advancements in semiconductor technology.

- <u>Industrial Engineering</u>: Evaluating, procuring, and integrating new tools and processes to enable tighter tolerance manufacturing at continually shrinking scales.

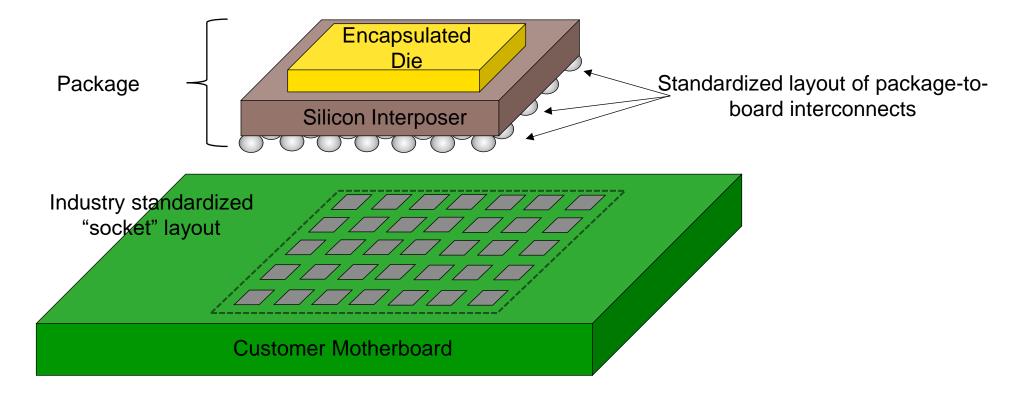

#### **Introduction to Packaging**

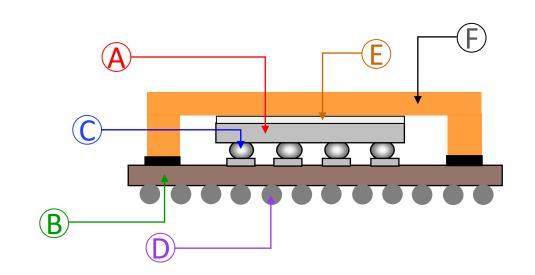

A) Silicon Die

Semiconductor Memory

C) Secondary (die-to-package) Interconnects

D) Primary (package-to-board) Interconnects

• Wire bonds, bumps, or pillars

Leads or solder balls

•

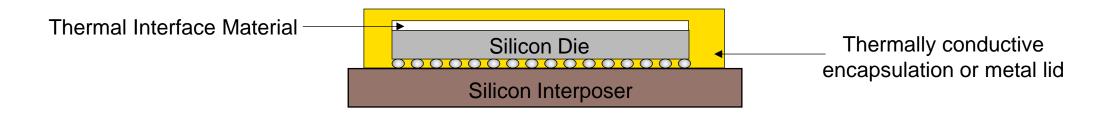

E) Heat Dissipation

- Heat sinks/spreaders

- Thermal Interface

Materials

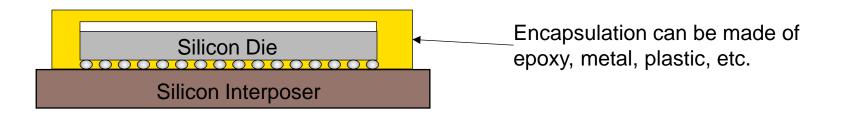

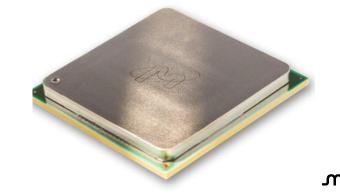

#### F) Environmental Protection

- Plastic/ epoxy seal

- Ceramic/ metal lid

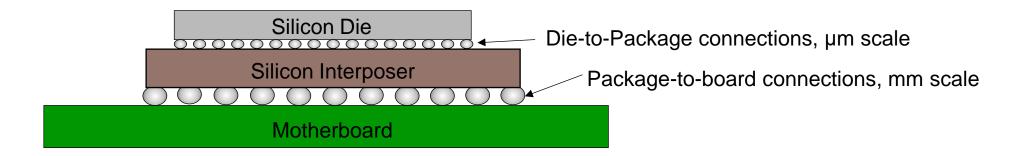

B) Interposer

- Die support

- Embedded interconnects

- 1. Electrical interface between the chip and outer circuitry:

- Can "adapt" between the different scale size of metal connections on the die to wires on circuit.

- Improves the quality of signal transmission.

- 2. Physical protection of die:

- Thinly diced silicon die are fragile and susceptible to mechanical stresses and environmental contamination.

<u>Plastic Encapsulation</u>: Injection molding process encases the assembled die in rigid plastic. <u>Metal Lid</u>: Assembled die is sealed under a metal lid.

- 3. Heat dissipation:

- Complex integrated circuits produce a lot of heat that can burn up a die without the heat dissipation of the package.

<u>Thermally Conductive Fillers:</u> Thermally conductive encapsulation materials can help conduct heat away from the die.

<u>Heat Spreader</u>: Metal lids can also effectively spread heat across a greater surface area.

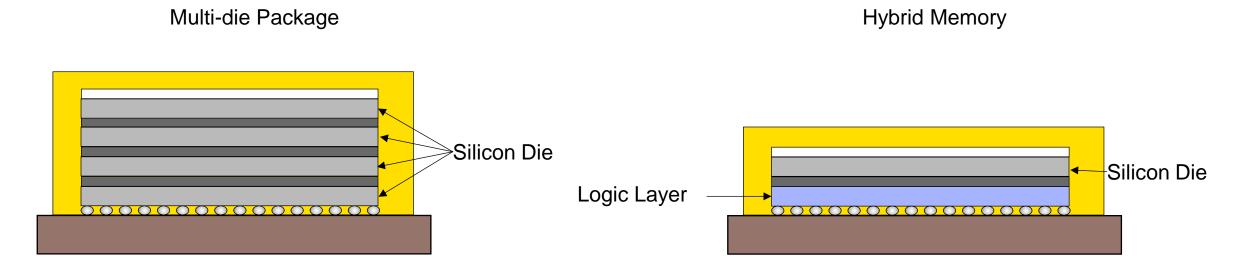

- 4. Expand functionality:

- Stack die to multiply the available memory.

- Increase functionality by including logic or different types of memory.

5. Customer ease of use:

• Standardized sockets allow for quick attachment, replacement, or upgrade of products.

#### **Introduction to Packaging**

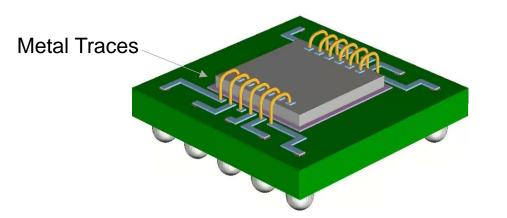

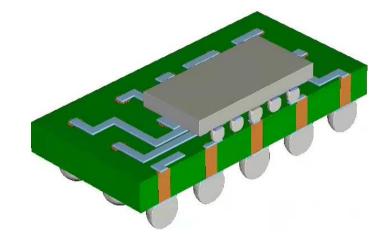

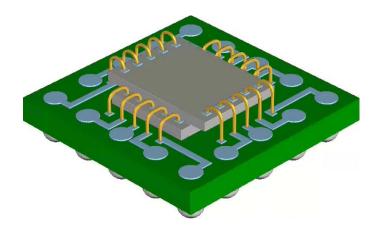

In the process of fabricating die, chemical and laser etchings expose connections on the <u>top</u> of die. To make an electrical connection, wires can be bonded to these connections on the top, or the die can be inverted ("flipped") to apply bonds to the bottom.

<u>Wire bond</u>: Very thin wires (usually gold) connect bond pads on the die to metal traces on the interposer. Over 80% of integrated circuits use wire bond. Flip Chip: Die is inverted. Solder balls on the die are directly bonded to metal pads on the package substrate.

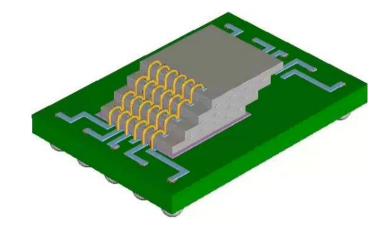

#### Wire bonded Package

Utilize wires bonded to pads on the top of the die down to pads on the substrate.

- Cheaper, easier fabrication process.

- Adaptable to different chip sizes and other package design considerations.

- Requires a larger overall package.

- Long wires result in greater parasitic voltage loss, slower signal transmission.

<u>Wire bond – Direct</u>: Wire bond is used to connect each die directly to the assembly substrate.

<u>Wire bond - Cascading</u>: Wire bonds cascade from one die to the next, ending at the substrate.

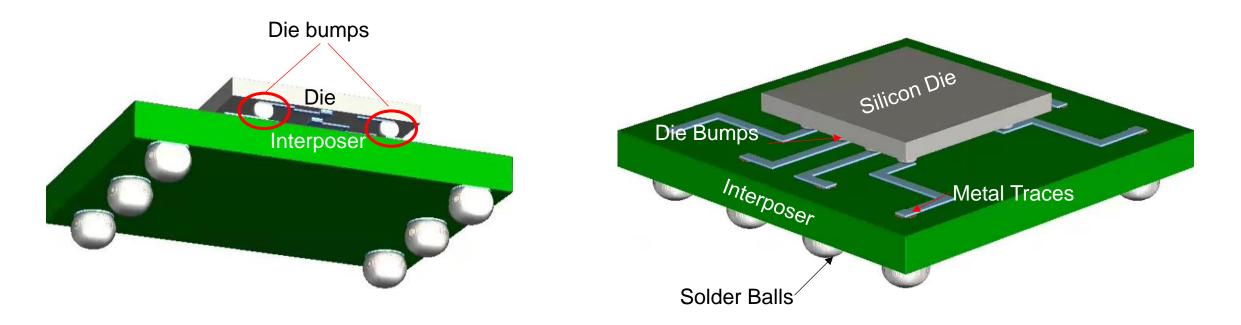

### **Bumped Package**

Solder ball "bumps" make electrical connections between metal pads on bonding surfaces.

- More complex fabrication process, increased cost compared to wire bonds.

- Changes to chip size and other package designs often require re-designing the bonding pattern.

- Small electrical connections result in far lower parasitic voltage loss.

- Enables high density interconnects and shrinks overall package size.

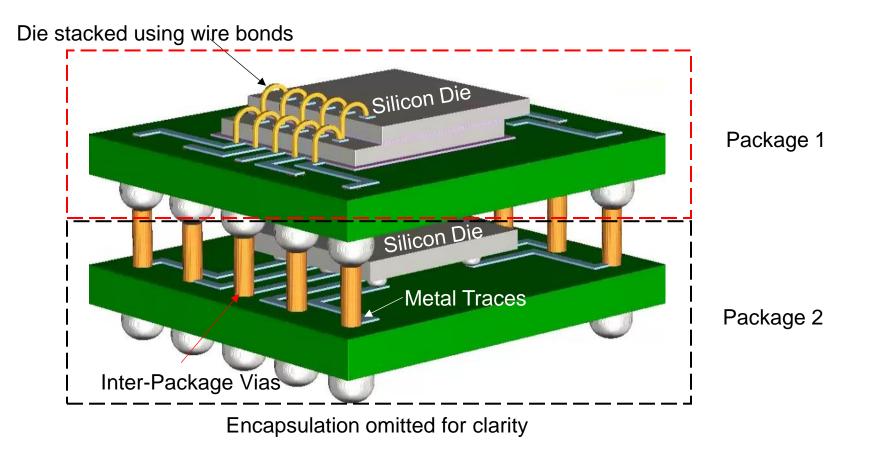

#### Package-on-Package

"Bumped" die are not easily stacked. Can expand memory then by stacking entire packages. Enables blended bonding types as well.

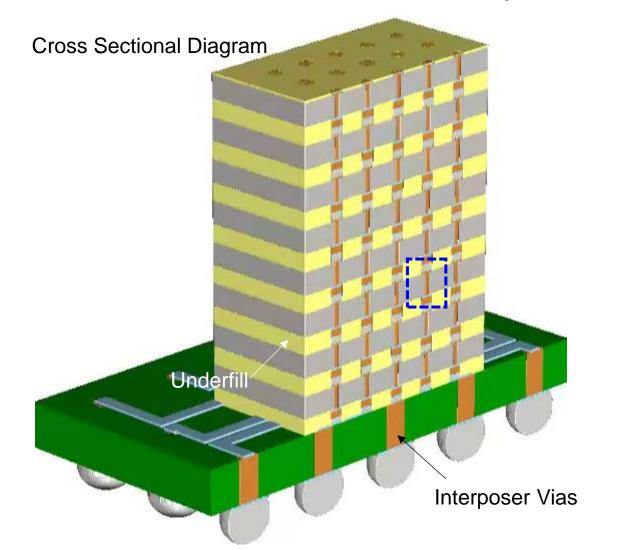

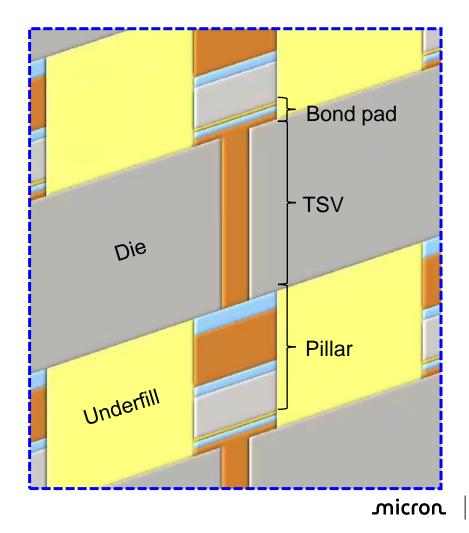

### Through Silicon Vias (TSV's)

Newer fabrication technique runs metal pillars or "vias" through the thickness of the die. Electrically connects the die and bonds to the interposer.

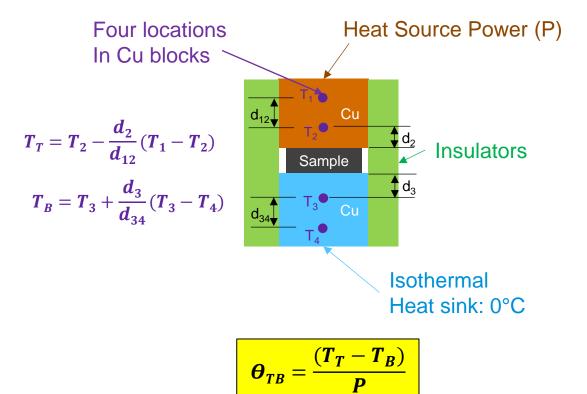

#### **Thermal Simulation**

Thermal modeling is a powerful tool for predicting how packages will perform while in different situations.

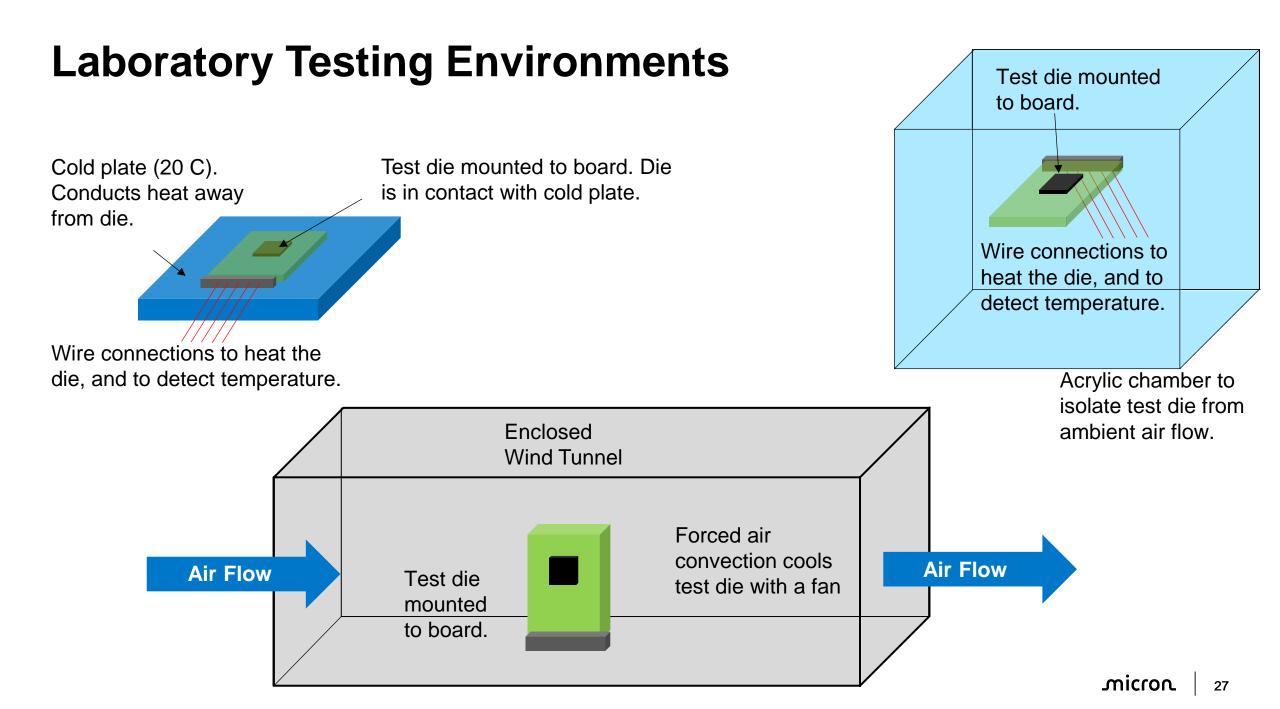

### **Laboratory Testing**

Computer simulations require comparison to experimental data for validation.

# Key Terminology Glossary

#### Glossary

| Term or acronym | Definition/description                                                                                                                                                                         |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BGA             | Ball Grid Array. Package type that utilizes an array of solder balls for electrical connection.                                                                                                |

| Bumped Package  | A package that uses solder ball "bumps" to make electrical connections between metal pads on bonding surfaces.                                                                                 |

| CSP             | Chip Scale Package. Package type where the finished package is not more than 1.1x the die size (almost the same size as the die).                                                              |

| DIP             | Dual Inline Package. Package type consisting of two parallel rows of pins.                                                                                                                     |

| eMMC            | Managed Memory Chip. An MCP (Multi-Chip Package) that includes a logic controller and one or more memory die.                                                                                  |

| F2F             | Face to Face. Package type consisting of two die mounted face to face and connected together via bumps.                                                                                        |

| FP              | Flat Package. A package with leads parallel to base plane attached on two opposing sides of the package periphery.                                                                             |

| НВМ             | High Bandwidth Memory. Multi DRAM memory package that uses 3D Stacking (vertical stacking of DRAM die utilizing TSVs and 3D Interconnects).                                                    |

| HMC             | Hybrid Memory Cube. This is a type of high-performance memory that uses a 3D architecture.<br>Multi-Chip Package (MCP) where two or more DRAM die are stacked directly on top of a logic chip. |

| Interposer      | Base that the die is mounted to in the package. Usually includes die-package interconnects.                                                                                                    |

#### Glossary

| Term or acronym | Definition/description                                                                                                                                                          |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PiP             | Package in Package. Two or more intermediate substrates, with die stacks on each, stacked and encapsulated into a single package                                                |

| PoP             | Package on Package. A method of stacking entire packages to expand memory. Two or more completed packages that are electrically connected together and behave as a single unit. |

| RDL             | Redistribution Layer. Additional interconnect layer(s) that resolve a mismatch between die and package interconnects.                                                           |

| Silicon Die     | The small piece of silicon that contains the integrated circuit. Silicon die is fragile and needs to be packaged.                                                               |

| SiP             | System in a Package. A complete system of interconnected die in one package.                                                                                                    |

| TSVs            | Through Silicon Vias. Metal pillars or "vias" that run through the thickness of the silicon die to electrically connect the die and bonds to the interposer.                    |

| Wirebond        | The packaging operation where very thin wires (usually gold) are used to make connections between the die bond pads and the package interconnects.                              |

# Document Updates

#### **Document Updates**

| Date            | Description                                                                                                                                                                                                                                                                       |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| January<br>2025 | <ul> <li>Added goals and objectives (slide 5)</li> <li>Added target audience (slide 6)</li> <li>Added semiconductor memory manufacturing flow (slide 9)</li> <li>Added several new images</li> <li>Added acronym legends</li> <li>Added glossary section (slide 28-30)</li> </ul> |

# **Educator Hub**

### micron

© 2024–2025 Micron Technology, Inc. All rights reserved. Information, products, and/or specifications are subject to change without notice. All information is provided on an "AS IS" basis without warranties of any kind. Statements regarding products, including statements regarding product features, availability, functionality, or compatibility, are provided for informational purposes only and do not modify the warranty, if any, applicable to any product. Drawings may not be to scale. Micron, the Micron logo, and other Micron trademarks are the property of Micron Technology, Inc. All other trademarks are the property of their respective owners.