Login / Register

We at Micron often feel like the advance guard as the tech industry marches ever closer to a major revolution in next-generation computing. To extract value and insights from the massive amounts of data being generated in the world today, that revolution will take advanced memory, along with additional compute power.

Today’s system architects understand that DDR4 SDRAM has hit a wall of 3200 MT/s while CPU core counts continue to increase. So, continued gains in compute performance require a high-performance memory to maintain available bandwidth per CPU core. Adding cores with DDR4 actually results in bandwidth per CPU core declining.

JEDEC announced the standard for fifth-generation double data rate (DDR5) SDRAM in July 2020 to address the need for higher bandwidth and massive improvements over previous generations of SDRAM. DDR5 is the most technologically advanced DRAM to date, enabling the next generation of server workloads by delivering more than an 85% increase in memory performance at the introduction data rate of 4800 MT/s. DDR5 will continue on to enable greater than double the data rates and effective bandwidth when compared to DDR4, fueling the increasing CPU core counts needed to enable year-over-year compute gains.

Opportunities and concerns arise with a new memory technology

A major transition in memory technology can trigger many questions and challenges for adopters and developers as new features and functionality are introduced. How will thermals compare? How can a designer get access to functional models for simulation? What are key technical differences to consider? Because DDR5 is such a different animal from DDR4, architects and designers are finding they must think differently about DDR5 adoption, or bring up.

Here are some examples:

- For improved efficiency and stability DDR5 modules introduce local voltage regulation with a power management integrated circuit (PMIC), which has historically been done on the motherboard.

- DDR5 modules introduce two 40-bit independent channels per DIMM enabled by burst length 16, while DDR4 used just one 72-bit channel per DIMM and burst length 8.

- DDR5 modules introduce a registered clock driver (RCD) that provides separate clock and address resources to each independent channel on the DIMM.

- DDR5 introduces decision feedback equalization (DFE) to mitigate the effects of inter-symbol interference (ISI) at higher data rates.

- DDR5 includes improved refresh schemes (Same Bank Refresh) to help further increase performance by targeting one bank per bank group.

Watch the podcast “Why Micron DDR5 DRAM Is More Than a Leap in Raw Bandwidth” with Rebecca Lewington and myself

Watch the podcast “Why Micron DDR5 DRAM Is More Than a Leap in Raw Bandwidth” with Rebecca Lewington and myself

Micron’s unique ecosystem for DDR5 collaboration grows rapidly

Micron was one of the first to sample DDR5 with data center customers, but we saw there was a deeper need. “As a lead developer of DDR5 specifications, Micron saw the opportunity early in DDR5 standards development,” said Micron’s CEO, Sanjay Mehrotra. “This is why we launched the DDR5 Technology Enablement Program (or TEP) to help get the entire ecosystem ready for DDR5 platform integration and optimization.”

The Micron DDR5 TEP, announced a year ago with a handful of ecosystem partners that included Cadence, Montage, Rambus, Renesas and Synopsys, is the first and only one of its kind in the industry. It has now grown to over 250 members from more than 100 companies. Many leaders in areas such as ecosystem and IP enablement, system integration, system architecture, and CPU and ASIC design have joined and are working to ensure a smooth transition to DDR5.

We’re proud of the way the ecosystem is actively supporting Micron’s DDR5 TEP “one-stop-shop” where all the key technical content is at the fingertips of developers and adopters. Micron is providing early access to technical information, support, and electrical and thermal models. Not just that, but Micron has also seeded DDR5 sample products through this program to aid in industry design, development, and growth of computing platforms.

The DDR5 TEP encourages discovery and development of next-generation products

Hyperscalers, large server companies, and PC OEMs are already integrating DDR5, so it’s expected that workloads using DDR4 now will migrate to DDR5. But these new systems don’t just appear overnight. DDR5 memory holds great promise; that’s why Micron created the TEP — to enable partners to draw on ecosystem collaboration to streamline design and integration challenges.

What’s also interesting to me is how, as the DDR5 technology matures and TEP membership expands, the needs of the TEP are shifting and we’re making new information available. In this transition to DDR5 memory, members of the TEP may well find their own interests and memory need to evolve as well.

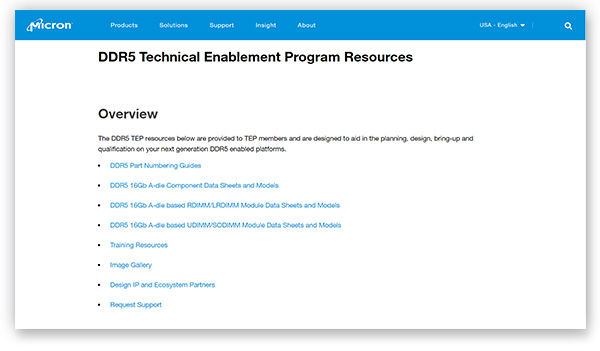

TEP Resources page, bringing the performance of DDR5 to the ecosystem

TEP Resources page, bringing the performance of DDR5 to the ecosystem

The TEP is a one-stop shop for DDR5 design and documents

Micron is deeply committed to the success of this important jump in system memory. We’ve made it easy and accessible to find materials to integrate DDR5 into partners’ systems and platforms. Once membership in the program is approved, members receive:

- Technical resources such as data sheets, thermal, and functional simulation models to aid in product development and platform bring-up

- Select DDR5 component and module samples as they become available

- Connection with other ecosystem partners that can aid in the design and bring up of DDR5 enabled platforms

- Technical support and training materials

Given the enthusiastic reception of DDR5 DRAM standards, the realization of how major and potentially disruptive this high-performance new memory will be, and the amazing growth of the Micron DDR5 TEP ecosystem, I predict great things are in store. Capture your own spot in the upcoming revolution!

Bringing DDR5-based products to market or evaluating a DDR5-enabled platform? Join us and apply for a Micron DDR5 TEP membership.